# Target Support Package™ FM5 2

User's Guide

#### How to Contact The MathWorks

www.mathworks.com

comp.soft-sys.matlab

www.mathworks.com/contact TS.html Technical Support

Web

Newsgroup

suggest@mathworks.com bugs@mathworks.com doc@mathworks.com

service@mathworks.com info@mathworks.com

Product enhancement suggestions

Bug reports

Documentation error reports

Order status, license renewals, passcodes Sales, pricing, and general information

508-647-7000 (Phone)

508-647-7001 (Fax)

The MathWorks, Inc. 3 Apple Hill Drive Natick, MA 01760-2098

For contact information about worldwide offices, see the MathWorks Web site.

Target Support Package™ FM5 User's Guide

© COPYRIGHT 2002–2008 by The MathWorks, Inc.

The software described in this document is furnished under a license agreement. The software may be used or copied only under the terms of the license agreement. No part of this manual may be photocopied or reproduced in any form without prior written consent from The MathWorks, Inc.

FEDERAL ACQUISITION: This provision applies to all acquisitions of the Program and Documentation by, for, or through the federal government of the United States. By accepting delivery of the Program or Documentation, the government hereby agrees that this software or documentation qualifies as commercial computer software or commercial computer software documentation as such terms are used or defined in FAR 12.212, DFARS Part 227.72, and DFARS 252.227-7014. Accordingly, the terms and conditions of this Agreement and only those rights specified in this Agreement, shall pertain to and govern the use. modification, reproduction, release, performance, display, and disclosure of the Program and Documentation by the federal government (or other entity acquiring for or through the federal government) and shall supersede any conflicting contractual terms or conditions. If this License fails to meet the government's needs or is inconsistent in any respect with federal procurement law, the government agrees to return the Program and Documentation, unused, to The MathWorks, Inc.

#### **Trademarks**

MATLAB and Simulink are registered trademarks of The MathWorks, Inc. See www.mathworks.com/trademarks for a list of additional trademarks. Other product or brand names may be trademarks or registered trademarks of their respective holders.

#### **Patents**

The MathWorks products are protected by one or more U.S. patents. Please see www.mathworks.com/patents for more information.

# **Revision History**

| March 2002     | Online only | New for Version 1.0 (Release 12.1+)       |

|----------------|-------------|-------------------------------------------|

| July 2002      | Online only | Revised for Version 1.0.1 (Release 13)    |

| December 2002  | Online only | Revised for Version 1.1 (Release 13+)     |

| June 2004      | Online only | Revised for Version 2.0 (Release 14)      |

| October 2004   | Online only | Revised for Version 2.0.1 (Release 14SP1) |

| March 2005     | Online only | Revised for Version 2.0.2 (Release 14SP2) |

| September 2005 | Online only | Revised for Version 2.0.3 (Release 14SP3) |

| March 2006     | Online only | Revised for Version 2.0.4 (Release 2006a) |

| September 2006 | Online only | Revised for Version 2.0.5 (Release 2006b) |

| March 2007     | Online only | Revised for Version 2.1 (Release 2007a)   |

| September 2007 | Online only | Revised for Version 2.2 (Release 2007b)   |

| March 2008     | Online only | Revised for Version 2.2.1 (Release 2008a) |

# **Getting Started**

| ۱ | ١ |   |  |

|---|---|---|--|

|   | ı | ١ |  |

|   |   | ı |  |

| Product Overview Introduction                           | 1-3<br>1-3 |

|---------------------------------------------------------|------------|

| Feature Summary                                         | 1-3        |

| Product                                                 | 1-6        |

| Additional Blocks on MATLAB Central Web Site            | 1-10       |

| Prerequisites                                           | 1-11       |

| Using This Guide                                        | 1-12       |

| Installation                                            | 1-13       |

| Hardware and Software Requirements                      | 1-14       |

| Operating System Requirements                           | 1-14       |

| Hardware Requirements                                   | 1-14       |

| Software Requirements                                   | 1-15       |

| Setting Up and Verifying Your Installation              | 1-17       |

| Setting Target Preferences                              | 1-18       |

| Configuring the Target Support Package™ FM5 Product for |            |

| Your Cross-Development Toolchain                        | 1-18       |

| Run Test Program                                        | 1-25       |

| Download Boot Code to Flash Memory                      | 1-25       |

| Start Menu Options                                      | 1-28       |

| Data Type Support and Scaling for Device Driver         | 1.00       |

| Blocks                                                  | 1-30       |

# **Generating Stand-Alone Real-Time Applications**

|   | -  |

|---|----|

|   | 2  |

| 4 | ø, |

| _ | _  |

|   |    |

| Overview 2-                                                     | 3   |

|-----------------------------------------------------------------|-----|

| Generating Real-Time Applications 2-                            | 3   |

| Deploying Generated Code 2-                                     | 4   |

|                                                                 |     |

| Tutorial: Creating a New Application 2-                         | .5  |

| Tutorial Overview                                               | 5   |

| Before You Begin                                                | 6   |

| The Example Model 2-                                            | 7   |

| Generating Code 2-1                                             | 0   |

| Downloading the Application to RAM via Serial or CAN 2-1        | 2   |

| Downloading the Application to RAM via BDM 2-1                  | 6   |

| Downloading Boot and Application Code 2-1                       | o   |

| Downloading Boot and Application Code2-1RAM vs. Flash Memory2-1 |     |

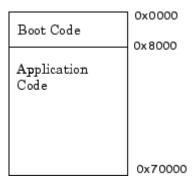

| Overview of Memory Organization and the Boot Process 2-2        |     |

| Downloading Application Code                                    |     |

| Stand-Alone Download Control Panel Utility 2-2                  |     |

| Downloading Boot or Application Code via CAN Without            | U   |

| Manual CPU Reset                                                | 7   |

| Rebuilding the Boot Code and Device Driver Libraries 2-2        |     |

| Running Applications with a Debugger 2-3                        | _   |

| 6 Pr                                                            |     |

| Parameter Tuning and Signal Logging 2-3                         | 2   |

| Methods for Parameter Tuning and Signal Logging 2-3             | 2   |

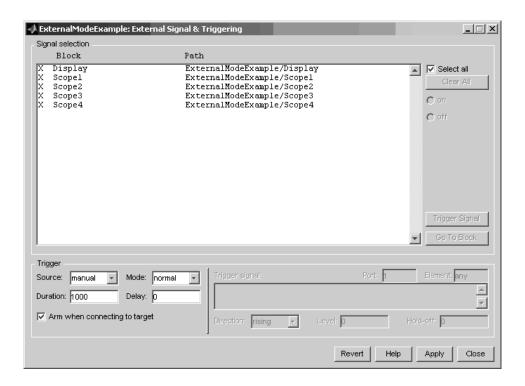

| Using External Mode 2-3                                         | 2   |

| Using a Third Party Calibration Tool 2-4                        | 1   |

| Data Acquisition (DAQ) List Configuration 2-4                   | 4   |

|                                                                 |     |

| HTML Code Profile (RAM/ROM) Report 2-4                          | 6   |

|                                                                 |     |

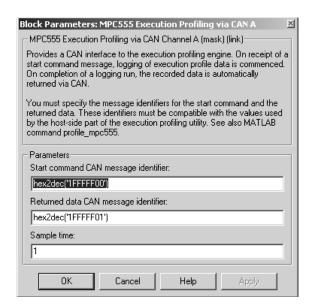

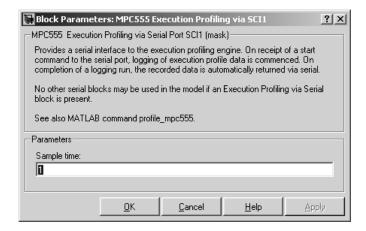

| Execution Profiling 2-4                                         |     |

| Overview of Execution Profiling 2-4                             |     |

| The Profiling Command 2-4                                       | _   |

| Execution Profiling Definitions                                 |     |

| MPC5xx Options for Execution Profiling 2-5                      |     |

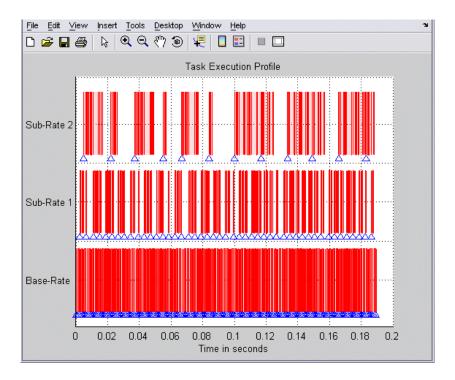

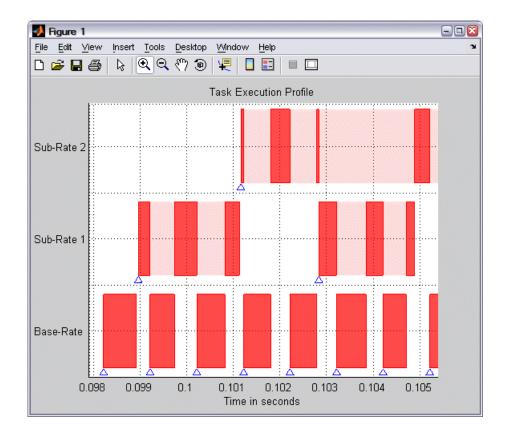

| Interpreting the Execution Profiling Graphic 2-5                | 3   |

| Enabling Execution Profiling for Device Driver Interrupt        | . F |

| Code Generation Options                             | 2  |

|-----------------------------------------------------|----|

| Requirements and Restrictions                       | 2  |

| Performance Tips                                    | 2  |

| Run the Model Advisor                               | 2  |

| Increase the System Clock Beyond the Default 20 MHz | 2  |

| Use Flash Instead of RAM                            | 2  |

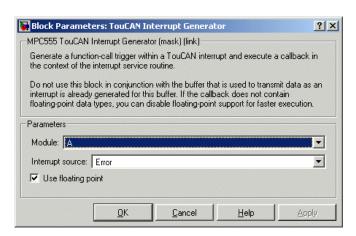

| TouCAN Interrupt Generator Block Performance Tips   | 2  |

| Optimized Target Function Library                   | 2  |

|                                                     |    |

| PIL Cosimula                                        | ti |

| One considers of DIL Continue lating                |    |

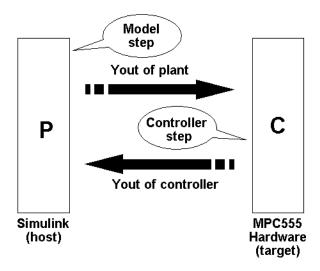

| Overview of PIL Cosimulation                        |    |

|                                                     |    |

| Why Use Cosimulation?                               |    |

| How Cosimulation Works                              |    |

| Tutorial 1: Building and Running a PIL              |    |

| Cosimulation                                        |    |

| Before You Begin                                    |    |

| Hardware Connections                                |    |

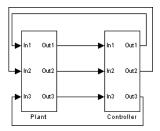

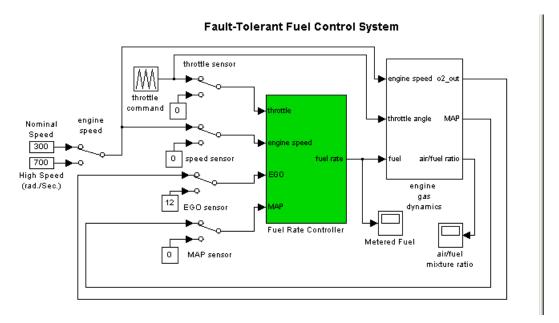

| The Demo Model                                      |    |

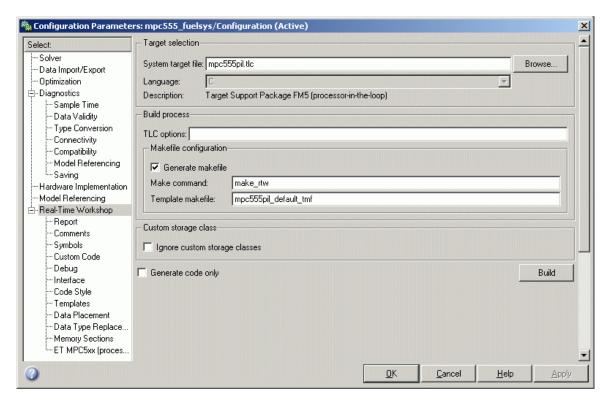

| Setting Up the Model                                | 3  |

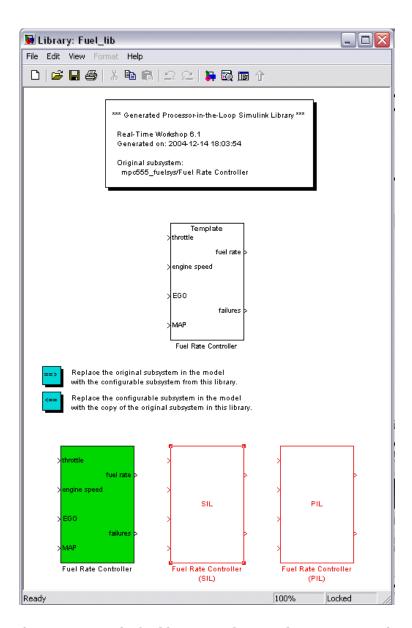

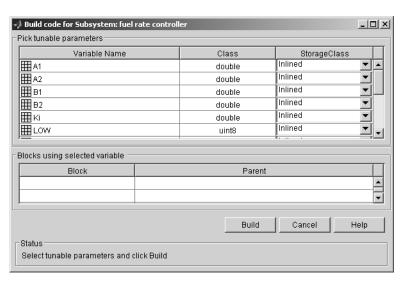

| Building PIL and Simulation Components              | 3  |

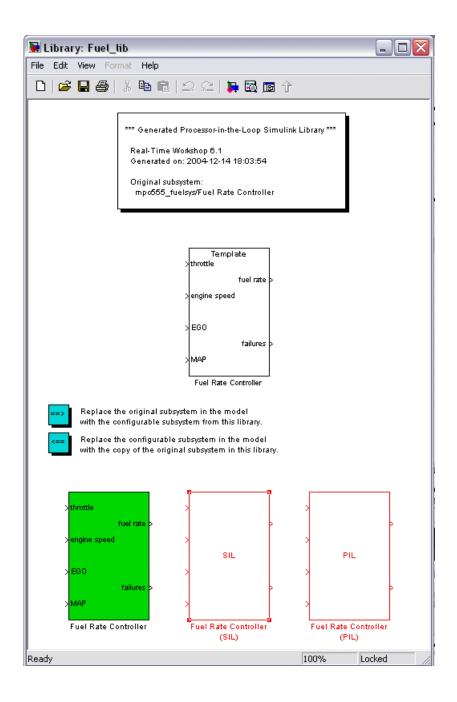

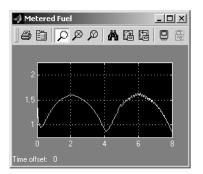

| Using the Demo Model In a PIL Cosimulation          | 3  |

| Modifying the Controller Subsystem                  | S  |

|                                                     |    |

| Tutorial 2: Using the Demo Model in Simulation      | 3  |

| Closed-Loop Simulation                              | 3  |

| SIL Simulation                                      | 9  |

| PIL Target Summary                                  | 3  |

| Code Generation Options                             | 3  |

| Build Process Files and Directories                 | 3  |

| Restrictions                                        | 3  |

| 10000110010110                                      | •  |

| Almostal on Francisch Woodst                        | £  |

| Algorithm Export Target                             | 3  |

| Block Reference                                             |

|-------------------------------------------------------------|

| rivers 4                                                    |

| ivers                                                       |

| el Blocks                                                   |

| B Controller Module (TouCAN)                                |

| e-64 4                                                      |

| n Profiling 4                                               |

| ts                                                          |

| Input/Output System (MIOS1)                                 |

| Analog-to-Digital Converter Module-64 4 ocessor Unit (TPU3) |

| ommunications Interface (SCI)                               |

| 4                                                           |

| age Blocks and CAN Drivers                                  |

| Blocks — Alphabetical Li                                    |

| Configuration Paramete                                      |

|                                                             |

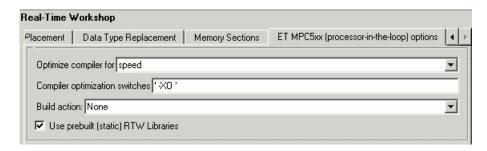

| Real-Time Workshop Pane: ET MPC5xx                                                                                                                                                                                                              |                          |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|

| (Processor-in-the-Loop) Options                                                                                                                                                                                                                 | 6-5                      |

| ET MPC5xx (Processor-in-the-Loop) Options Tab                                                                                                                                                                                                   |                          |

| Overview                                                                                                                                                                                                                                        | 6-5                      |

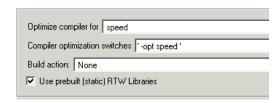

| Optimize compiler for                                                                                                                                                                                                                           | 6-6                      |

| Compiler optimization switches                                                                                                                                                                                                                  | 6-7                      |

| Build action                                                                                                                                                                                                                                    | 6-8                      |

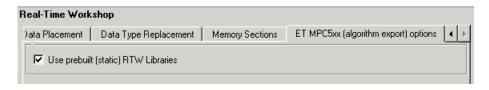

| Use prebuilt (static) RTW Libraries                                                                                                                                                                                                             | 6-9                      |

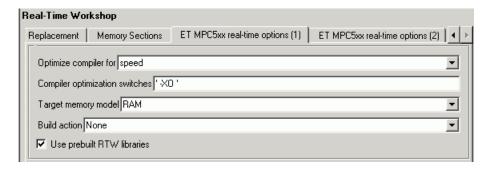

| Real-Time Workshop Pane: ET MPC5xx Real-Time                                                                                                                                                                                                    |                          |

| Options (1)                                                                                                                                                                                                                                     | 6-10                     |

| ET MPC5xx Real-Time Options (1) Tab Overview                                                                                                                                                                                                    | 6-10                     |

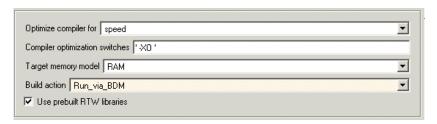

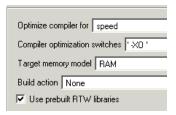

| Optimize compiler for                                                                                                                                                                                                                           | 6-11                     |

| Compiler optimization switches                                                                                                                                                                                                                  | 6-12                     |

| Target Memory Model                                                                                                                                                                                                                             | 6-13                     |

| Build action                                                                                                                                                                                                                                    | 6-15                     |

| Use prebuilt RTW libraries                                                                                                                                                                                                                      | 6-16                     |

| Real-Time Workshop Pane: ET MPC5xx Real-Time                                                                                                                                                                                                    |                          |

| Options (2)                                                                                                                                                                                                                                     | 6-17                     |

| ET MPC5xx Real-Time Options (2) Tab Overview                                                                                                                                                                                                    | 6-17                     |

| Maximum number of concurrent base-rate overruns                                                                                                                                                                                                 | 6-17                     |

| Maximum number of concurrent sub-rate overruns                                                                                                                                                                                                  | 6-18                     |

| Execution profiling                                                                                                                                                                                                                             | 6-20                     |

| Number of data points                                                                                                                                                                                                                           | 6-20                     |

|                                                                                                                                                                                                                                                 |                          |

| Toolchains and Hardy                                                                                                                                                                                                                            | vare                     |

| Toolchains and Hardy Setting Up Your Toolchain                                                                                                                                                                                                  | vare<br>A-3              |

| Setting Up Your Toolchain Setting Up Your Installation with Wind River Compiler                                                                                                                                                                 | A-3                      |

| Setting Up Your Toolchain<br>Setting Up Your Installation with Wind River Compiler<br>and Wind River Systems SingleStep™ Debugger                                                                                                               | A-3                      |

| Setting Up Your Toolchain                                                                                                                                                                                                                       | A-3<br>A-4<br>A-4        |

| Setting Up Your Toolchain<br>Setting Up Your Installation with Wind River Compiler<br>and Wind River Systems SingleStep™ Debugger                                                                                                               | A-3                      |

| Setting Up Your Toolchain  Setting Up Your Installation with Wind River Compiler and Wind River Systems SingleStep <sup>TM</sup> Debugger  Required Hardware and Software  Procedure  Setting Up Your Installation with Freescale <sup>TM</sup> | A-3<br>A-4<br>A-4<br>A-4 |

| Setting Up Your Toolchain  Setting Up Your Installation with Wind River Compiler and Wind River Systems SingleStep™ Debugger  Required Hardware and Software                                                                                    | A-3<br>A-4<br>A-4        |

| A-14 A-20 A-20 A-20 Iardware A-22 A-22               |

|------------------------------------------------------|

| A-14 A-20 A-20 Cion Channels A-20 Iardware A-22 A-25 |

| A-20                                                 |

| A-20 ion Channels A-20 Iardware A-22 A-25            |

| A-20         Iardware       A-22         A-25        |

| Iardware A-22                                        |

| A-22                                                 |

|                                                      |

|                                                      |

|                                                      |

| A-26                                                 |

| <b>A-26</b> ectory Structure and                     |

| A-2"                                                 |

|                                                      |

| Examples                                             |

| Examples B-2                                         |

| <del>-</del>                                         |

# Getting Started

This section contains the following topics:

Product Overview (p. 1-3) Overview of the product and its use

in the development process.

Additional Blocks on MATLAB Additional resources such as Central Web Site (p. 1-10) user-contributed blocks.

Prerequisites (p. 1-11) What you need to know before using

the Target Support Package<sup>TM</sup> FM5

product.

Using This Guide (p. 1-12)

Suggested path through this

document to get you up and running quickly with the Target Support

Package FM5 product.

Installation (p. 1-13) Installation of the product.

Hardware and Software Requirements (p. 1-14)

Hardware platforms supported by the product; required MathWorks tools and development tools (e.g., compilers, debuggers) required for

use with the product.

Setting Up and Verifying Your

Installation (p. 1-17)

Overview of setting up your development tools and hardware to work with the Target Support Package FM5 product, and verifying

correct operation.

Setting Target Preferences (p. 1-18) Configuring environmental settings

and preferences for use with specific

development tools.

Start Menu Options (p. 1-28)

Data Type Support and Scaling for Device Driver Blocks (p. 1-30)

A quick guide to the functionality available in the Start menu.

Input and output data types supported by the device driver blocks.

# **Product Overview**

#### In this section...

"Introduction" on page 1-3

"Feature Summary" on page 1-3

"Applications for the Target Support Package™ FM5 Product" on page 1-6

### Introduction

The Target Support Package™ FM5 product is an add-on product for use with the Real-Time Workshop® Embedded Coder™ software. It provides a complete and unified set of tools for developing embedded applications for the Freescale™ MPC555 and MPC56x processors (MPC561, MPC562, MPC563, MPC564, MPC565 and MPC566). The MPC5xx family of processors are products of Freescale Semiconductor, Inc., formerly a division of Motorola, Inc.

Used in conjunction with the Simulink®, Stateflow®, and Real-Time Workshop Embedded Coder products, Target Support Package FM5 software lets you

- Design and model your system and algorithms.

- Compile, download, run and debug generated code on the target hardware, seamlessly integrating with industry-standard compilers and development tools for the MPC5xx.

- Use cosimulation and rapid prototyping techniques to evaluate performance and validate results obtained from generated code running on the target hardware.

- Deploy production code on the target hardware.

# **Feature Summary**

### **Production Code Generation**

• The Real-Time Workshop Embedded Coder product generates production code for use on the target MPC5xx microcontroller.

- The Real-Time Workshop Embedded Coder product generates project or makefiles for popular cross-development systems:

- Wind River Systems Wind River Compiler

- Freescale CodeWarrior®

- Debugger support:

- Wind River Systems SingleStep™ debugger

- Freescale CodeWarrior debugger

- Support for ANSI C (ANSI X3.159-1989) math library for floating-point functions.

## **Device Driver Support**

- The Target Support Package FM5 Library provides device driver blocks that let your applications access on-chip resources. The I/O blocks support the following features of the MPC555 and MPC56x:

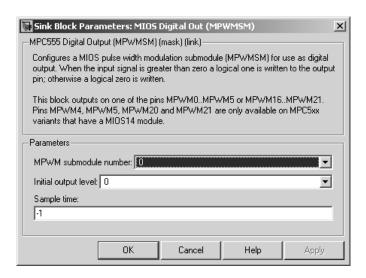

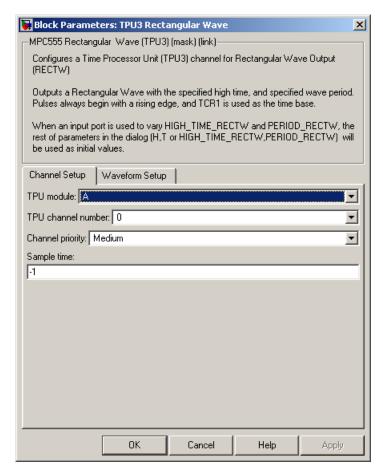

- Pulse width modulation (PWM) generation via the Modular Input/Output Subsystem (MIOS) PWM unit or the Time Processor Unit 3 (TPU) modules

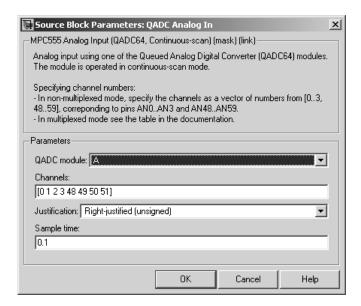

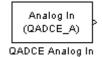

- Analog input via the Queued Analog-to-Digital Converter (QADC64)

- Digital input and output via the MIOS or TPU

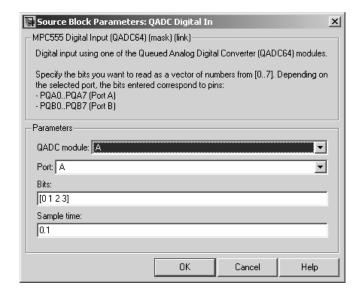

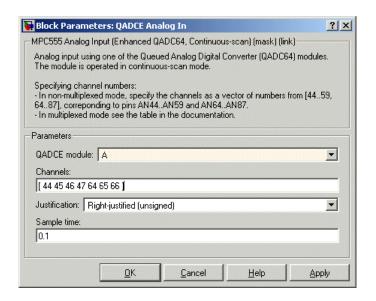

- Digital input via the QADC64

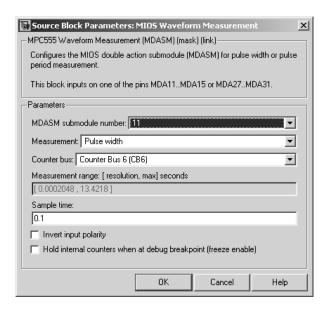

- Frequency and pulse width measurement via the MIOS Double Action Submodule (MDASM)

- Transmit or receive Controller Area Network (CAN) messages via the MPC5xx TouCAN modules

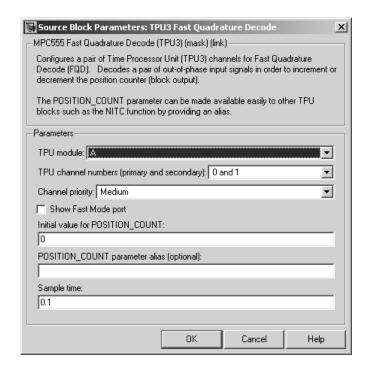

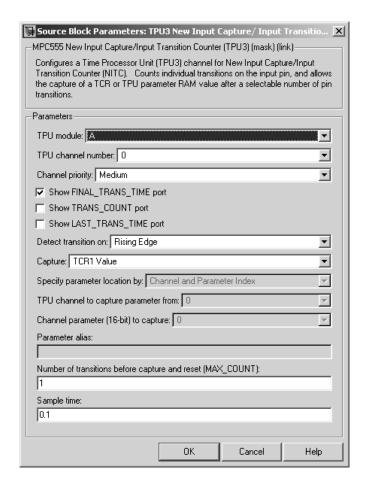

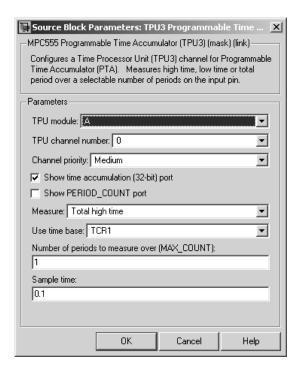

- Driver blocks to support other functions of the TPU modules Fast Quadrature Decode, New Input Capture/Input Transition Counter, and Programmable Time Accumulator

- Serial transmit and receive

- Utility blocks such as a watchdog timer

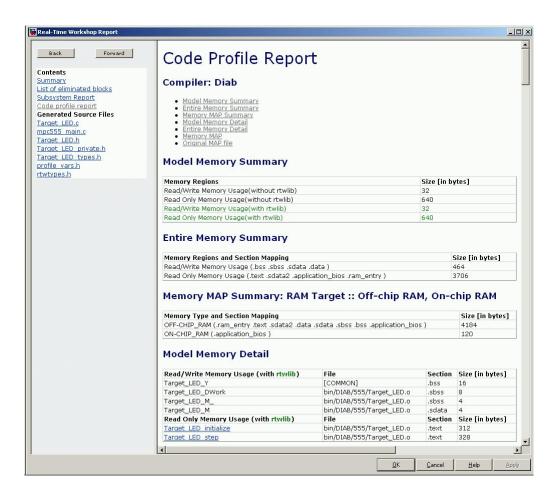

### **Code and Performance Analysis**

Web-viewable code generation report includes

- Analysis of RAM/ROM usage and other variables

- Analysis of code generation options used, with optimization suggestions

- Hyperlinks to all generated code files

- Hyperlinks from generated code to source model in Simulink

# **Applications Development and Rapid Prototyping**

- Generation of real-time, stand-alone code for MPC5xx

- Scheduler and time functions for singlerate or multirate real-time operation

- CAN-based loader for download of generated code to RAM or flash memory

- CAN-based host-target communications for non-real-time retrieval of data on host computer

#### Simulation and Cosimulation

- Automatic S-function generation lets you validate your generated code in software-in-the-loop (SIL) simulation.

- Processor-in-the-loop (PIL) cosimulation lets you integrate generated code, running on the target processor, into your simulation.

- SIL and PIL code components are generated by the Real-Time Workshop Embedded Coder product. These simulation components are in the same compact and efficient format as the production code generated for final deployment.

## **CAN Support**

- $\bullet\,$  Transmit or receive CAN messages via the MPC5xx TouCAN modules.

- CAN Drivers (Vector) library provides blocks for transmitting, receiving, configuring, and connecting to Vector-Informatik CAN hardware and drivers. These can be used in simulation to connect to a real CAN bus.

• The CAN Message Blocks library includes blocks for transmitting, receiving, decoding, and formatting CAN messages. It also supports message specification via the Vector-Informatik CANdb standard. CAN is an industry standard protocol used in automotive electronics and many other embedded environments where dispersed components require sharing of information.

## **Code Validation and Performance Analysis**

**Code Validation.** Since signal data is available to Simulink during each sample interval in a PIL simulation, you can observe signal data on Scope blocks or other Simulink signal viewing blocks. You can also store signal data to MAT-files via To File blocks. To validate the results obtained by the generated code running on the target processor, you can compare these files to results obtained using a normal Simulink plant/controller simulation.

**Determining Code Size.** In control design it is critical to ensure that the size of the generated code does not exceed physical limitations of RAM and ROM. The Target Support Package FM5 product can automatically produce a code generation report that displays the RAM usage and ROM size of the generated code.

This capability is useful when selecting which code generation optimizations will be used. After determining the size of the required RAM and ROM, you can consider which code generation optimizations to use, and consider modifications to the modeling style.

# Applications for the Target Support Package™ FM5 Product

The Target Support Package FM5 product provides targets that support three application scenarios:

- Real-time (RT) execution for production and rapid prototyping

- $\bullet \ \ Processor\text{-in-the-loop} \ (PIL) \ cosimulation \ target \\$

- Algorithm export (AE) target

In the sections that follow, we summarize typical applications and the tasks you will need to perform for each; we also provide links to the relevant documentation.

## **Real-Time Execution and Rapid Prototyping**

The Target Support Package FM5 real-time target enables you to use your controller block diagram in real time to perform embedded control. With this target, you can add I/O blocks for the MPC5xx to your controller subsystem, generate and build code, download to the target, and run the generated C code.

When you first begin using the RT target, see "Tutorial: Creating a New Application" on page 2-5, which demonstrates the following topics through the use of a simple model with a device driver:

- Examining the demo model with a plant model and controller

- Adding the MPC555 Resource Configuration block to your subsystem

- Adding I/O device drivers from the Target Support Package FM5 library

- Selecting the RT target

- Generating code for real time

- Downloading code with

- A BDM connector

- CAN

- Running the generated code in real-time

You may also be interested in generating code analysis information from your RT target build. See "HTML Code Analysis (RAM/ROM) Report" on page 3-28 for details.

## **Processor-in-the-Loop**

The processor-in-the-loop (PIL) target lets you run a cosimulation of a closed-loop Simulink model for the purpose of code validation and analysis. When running a PIL cosimulation, you use a closed-loop model with two major components: a plant model and a controller. The plant model may

contain any Simulink blocks including a combination of continuous-time and discrete-time blocks.

To get started with the PIL target, see "Tutorial 1: Building and Running a PIL Cosimulation" on page 3-6. The tutorial covers the following topics:

- Opening the demo model and examining the plant model and controller

- Selecting the PIL target

- Generating the Embedded Real-Time (ERT) S-function and the corresponding library block

- Inserting the S-function back into the closed-loop model

- · Automatic downloading of generated code with

- Wind River Systems SingleStep debugger and a Background Debug Mode (BDM) port connector

- CodeWarrior and a BDM connector

- Running a PIL cosimulation

You may also be interested in generating code analysis information from your PIL target build. See "HTML Code Analysis (RAM/ROM) Report" on page 3-28 for details.

## **Algorithm Export**

The Target Support Package FM5 algorithm export (AE) target enables you to generate code for your controller subsystem and build the code as a stand-alone executable for use on the MPC5xx. The difference between the AE and the PIL target is that the AE target eliminates all extraneous code (such as serial communications code) used for cosimulation, and also eliminates any real-time interrupts. The AE target therefore generates code only for the basic controller subsystem (e.g. algorithm code). You can then modify or customize this code for your own special purposes.

In contrast, the RT target provides turnkey code including interrupt service routines, driver code, and underlying initialization code for the MPC5xx. Depending upon your particular application, you may find it more valuable to begin with the AE target baseline, and extend this environment for your own use.

The AE target is documented in "Algorithm Export Target" on page 3-26.

Like the PIL and RT targets, the AE target supports generation of code analysis information. See "HTML Code Analysis (RAM/ROM) Report" on page 3-28 for details.

# **Additional Blocks on MATLAB Central Web Site**

Check the MATLAB Central Web site for user- and developer-contributed blocks and demos, such as the MPC555 Motor Control Function Blockset for Release 2006a.

The MPC555 Motor Control Function Blockset is an extensive collection of additional TPU I/O blocks for the Target Support Package<sup>TM</sup> FM5 product. This functionality is particularly useful in the context of motor and powertrain control, including functions for missing and additional tooth detection.

# **Prerequisites**

This document assumes you are experienced with the MATLAB®, Simulink®, Stateflow®, Real-Time Workshop®, and Real-Time Workshop® Embedded Coder™ products.

Minimally, you should read the "Getting Started" section of the Real-Time Workshop documentation to understand general concepts and terminology related to Real-Time Workshop software, and try some of the demos of the user interface, code generation and build process, and other essential features.

You should also familiarize yourself with the Real-Time Workshop Embedded Coder documentation.

In addition, if you want to understand and use the device driver blocks in the Target Support Package<sup>TM</sup> FM5 library, you should have at least a basic understanding of the architecture of the MPC5xx processor you are using. The Freescale<sup>TM</sup> MPC555 Users Guide (or MPC561-564, or MPC565-566, as appropriate) is required reading. We recommend that you read the introduction to the processor and familiarize yourself with all the major subsystems of the MPC5xx. You can find this document at the following URL: http://www.freescale.com/.

# **Using This Guide**

We suggest the following path to get acquainted with the Target Support Package™ FM5 product and gain hands-on experience with the features most relevant to your interests:

- Read Chapter 1, "Getting Started" in its entirety, paying particular attention to "Setting Up and Verifying Your Installation" on page 1-17.

- If you are interested in using the supplied device driver blocks and in deploying stand-alone, real-time applications on the MPC5xx, read Chapter 2, "Generating Stand-Alone Real-Time Applications" Work through the "Tutorial: Creating a New Application" on page 2-5.

- If you are interested in processor-in-the-loop (PIL) cosimulation, read Chapter 3, "PIL Cosimulation" to learn about the Target Support Package FM5 PIL target. Work through the "Tutorial 1: Building and Running a PIL Cosimulation" on page 3-6.

- Then, for in-depth information about the Target Support Package FM5 device drivers and other blocks, see Chapter 4, "Block Reference" It is particularly important to read MPC555 Resource Configuration, as the MPC555 Resource Configuration block is required to use most of the device driver blocks.

See also the Target Support Package FM5 Demos. To browse the demos, open the MPC555 Help and Demos library. You can then double click the **Help for Demos** block to go directly to information and instructions for all demos, or select **Start > Links and Targets > Target Support Package FM5 > Demos**. These demos are used in the tutorials, where there are detailed explanations.

# Installation

Your platform-specific MATLAB<sup>®</sup> Installation guide provides all of the information you need to install the Target Support Package™ FM5 product.

Prior to installing, you must obtain a License File or Personal License Password from The MathWorks. The License File or Personal License Password identifies the products you are permitted to install and use.

As the installation process proceeds, it displays a dialog where you can select which products to install.

# Hardware and Software Requirements

#### In this section...

"Operating System Requirements" on page 1-14

"Hardware Requirements" on page 1-14

"Software Requirements" on page 1-15

# **Operating System Requirements**

The Target Support Package<sup>TM</sup> FM5 product is a PC Microsoft<sup>®</sup>Windows<sup>®</sup> only product. The product has been tested on MicrosoftWindows XP.

You can see the MATLAB® system requirements online at

http://www.mathworks.com/support/sysreq/current release/index.html

# **Hardware Requirements**

Programs generated by the Target Support Package FM5 product can run on any Electronic Control Unit (ECU) that is based on the MPC555 or MPC56x (561-6) processor.

In this document, we specify settings and procedures for use with the Phytec phyCORE-MPC555 board, the Phytec MPC565, the Axiom MPC555, and the Axiom MPC564, in conjunction with specific cross-development environments, see "Setting Up Your Target Hardware" on page A-13 for details.

If you use a different development board, you may need to adapt these settings and procedures for your development board.

If you want to use CAN to transmit or receive CAN messages between your host PC and your target, you require Vector-Informatik CAN hardware supported by the Vector CAN Driver Library. See "CAN Hardware and Drivers" on page A-20.

# **Software Requirements**

## Required and Related MathWorks™ Products

The Target Support Package FM5 product requires these products from The MathWorks<sup>TM</sup>:

- MATLAB

- Simulink®

- Real-Time Workshop®

- Real-Time Workshop® Embedded Coder™

- Optional for Real-Time Target

- Required for Processor-in-the-Loop and Algorithm Export Targets.

- Required for CCP Data Acquisition (DAQ) List mode of operation.

For more information about any of these products, see either

- The online documentation for that product, if it is installed

- The MathWorks Web site, at http://www.mathworks.com; see the Products section

The MathWorks provides several products that are especially relevant to the kinds of tasks you can perform with the Target Support Package FM5 product. For required and related products, see: http://www.mathworks.com/products/target\_mpc555/

## **Supported Cross-Development Tools**

In addition to the required MathWorks software, a supported cross-development environment is required. The Target Support Package FM5 product currently supports the cross-development tools listed below; please read carefully the limitations noted:

- Freescale<sup>™</sup> CodeWarrior<sup>®</sup> Development Studio, MPC5xx Edition, v8.7 (debug via Macraigor Systems Wiggler, Raven/ Blackbird, or On-board BDM).

- Wind River Systems Wind River Compiler version 5.4.0, (formerly known as Diab), and Wind River Systems SingleStep™ debugger of the following versions:

- Wind River Systems SingleStep with vision Version 7.7.5 (debug via Wind River visionPROBE) (for MPC5xx)

- Wind River Systems SingleStep Version 7.6.6 (debug via Macraigor Systems Wiggler, Raven / Blackbird, On-board BDM) (for MPC555 only)

(+ Fromelf patch from Wind River Support)

You must download fromelf.exe for the Wind River Systems SingleStep debugger 7.6.6, otherwise builds with debug flag -g set will not load, with the following error: "aborting due to failure of ELF reader".

Note to use these BDM devices you must set up nondefault target preferences, as detailed in "Setting Up and Verifying Your Installation" on page 1-17.

The full feature set (PIL, RT, and AE targets) is supported for both toolchains.

Before using the Target Support Package FM5 product with any of the above cross-development tools, please be sure to read and follow the instructions in "Setting Up and Verifying Your Installation" on page 1-17.

See also this solution for Information about the availablity of SingleStep.

# **Setting Up and Verifying Your Installation**

The next sections describe how to configure your development environment (compiler, debugger, etc.) for use with the Target Support Package™ FM5 product and verify correct operation. The initial configuration steps are described in the following sections:

- You must set up your development environment and your target hardware.

Information on these settings can be found in the Appendix A, "Toolchains and Hardware":

- "Setting Up Your Target Hardware" on page A-13

- "Setting Up Your Toolchain" on page A-3

**Note** You MUST check your jumper settings. Incorrect operation or even hardware damage may occur if you do not. See "Jumper Settings" on page A-14.

- You must configure the Target Support Package FM5 product to work with your toolchain by specifying the locations of your compiler and debugger. This is described in the section "Setting Target Preferences" on page 1-18.

- We supply a test program to verify your installation. This confirms you have correctly set up your toolchain, target preferences and development board. See "Run Test Program" on page 1-25.

- The next step is to download boot code to the flash memory of your MPC5xx. See "Download Boot Code to Flash Memory" on page 1-25.

**Note** You must download the new boot code if you have used a previous release of the Target Support Package FM5 product with your hardware. See "Download Boot Code to Flash Memory" on page 1-25.

Once you have completed these steps we suggest you run the tutorials in subsequent sections to get started.

# **Setting Target Preferences**

#### In this section...

"Configuring the Target Support Package™ FM5 Product for Your Cross-Development Toolchain" on page 1-18

"Run Test Program" on page 1-25

"Download Boot Code to Flash Memory" on page 1-25

# Configuring the Target Support Package™ FM5 Product for Your Cross-Development Toolchain

This section describes how to set target preferences associated with the Target Support Package  $^{\text{TM}}$  FM5 product. These settings persist across MATLAB® sessions and different models. Target preferences let you specify the location of your MPC5xx cross-compiler, the communications port to be used for downloading code, and other parameters affecting the generation, building, and downloading of code.

You must make sure you localize the Target Support Package FM5 settings to suit your PC and cross-development toolchain. It is important that you set the correct path to your compiler and debugger using the **Target Support Package FM5 Target Preferences** dialog box.

Instructions for setting up specific third-party toolchains for use with the Target Support Package FM5 product are in Appendix A, "Toolchains and Hardware". Make sure you have followed the instructions to set up your toolchain first:

- "Setting Up Your Installation with Wind River Compiler and Wind River Systems SingleStep™ Debugger" on page A-4

- "Setting Target Preferences for Wind River Compiler and Wind River Systems SingleStep™" on page A-5. Note especially the settings you must change if you are not using the visionPROBE BDM device. The defaults are set up for the visionPROBE.

- "Setting Up Your Installation with Freescale™ CodeWarrior®" on page A-9

- "Set Target Preferences for CodeWarrior®" on page A-11

You can modify target preference objects via the **Target Support Package FM5 Target Preferences** dialog box:

1 Select Start > Links and Targets > Target Support Package FM5 > Target Preferences.

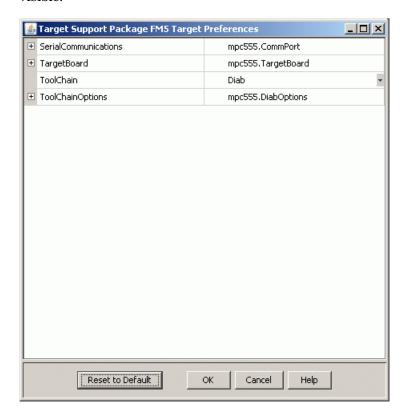

This opens the **Target Support Package FM5 Target Preferences** dialog box where you can edit the settings for your cross-development environment. When you first open the dialog the following settings are visible.

2 Select Diab or CodeWarrior from the drop-down Toolchain menu.

Note the Wind River Compiler was formerly known as Diab. Any appearances of the term *Diab* in the documentation and / or product should be understood to refer to the Wind River Compiler.

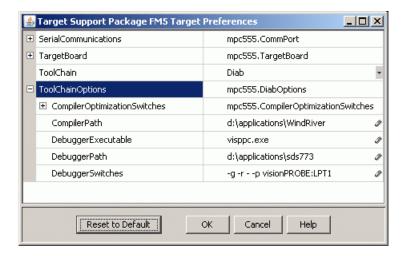

3 Expand **ToolChainOptions** as shown below (by clicking the plus sign) and type the correct path into **CompilerPath**. The following shows Wind River Compiler options. Note that the defaults are set up for the visionPROBE—see the Appendix for settings to use another BDM device, described in "Setting Target Preferences for Wind River Compiler and Wind River Systems SingleStep<sup>TM</sup>" on page A-5.

**Note** The drive designated in the compiler and debugger paths must be either an actual hard drive on your PC, or a mapped drive. Do not use a Universal Naming Convention (UNC).

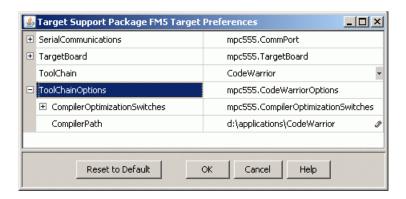

**4** For Wind River Systems SingleStep<sup>™</sup> you must also type the correct path into **Debugger Path**. This is not necessary for CodeWarrior<sup>®</sup> as the compiler and debugger are integrated. The example below shows the CodeWarrior preferences.

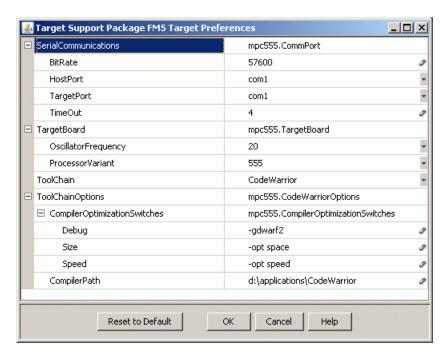

There are other settings in the target preferences you can see by expanding all the options, as shown.

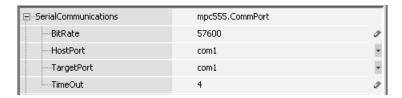

#### **Serial Communications**

These target preferences relate to Processor-in-the-Loop (PIL) cosimulation only.

- BitRate Bit rate (in bps) for host/target communications. The default is 57600.

- HostPort Host serial port for host/target communications. Select from com1 to com8; the default is com1.

- TargetPort Target board serial port for host/target communications. Select from com1 to com8; the default is com1.

- TimeOut Time-out value (in seconds) for the serial communications port.

The default is 4.

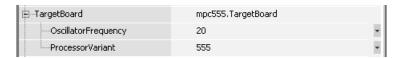

# **Target Board**

- OscillatorFrequency Choose either 20 MHz (the default) or 4 MHz if you are using a 4MHz board.

- ProcessorVariant Here you can select from 555, 561, 562, 563, 564, 565 or 566 to match your target processor. The default is the MPC555.

When you install bootcode after setting target preferences the correct bootcode for your chosen target processor and oscillator frequency will be automatically installed. Note that you also need to make these settings match in your models for the non-default target processor and oscillator frequency. See "Configuration for Nondefault Hardware" on page A-22.

## **Compiler Optimization Switches**

| ToolChain                      | Diab                                |

|--------------------------------|-------------------------------------|

| ToolChainOptions               | mpc555.DiabOptions                  |

| □ CompilerOptimizationSwitches | mpc555.CompilerOptimizationSwitches |

| Debug                          | -g                                  |

| Size                           | -XO -Xsize-opt                      |

| Speed                          | -XO                                 |

| CompilerPath                   | d:\applications\WindRiver           |

| DebuggerExecutable             | visppc.exe                          |

| DebuggerPath                   | d:\applications\sds773              |

| DebuggerSwitches               | -g -rp visionPROBE:LPT1             |

| ToolChain                      | CodeWarrior                         |

| ToolChainOptions               | mpc555.CodeWarriorOptions           |

| ☐ CompilerOptimizationSwitches | mpc555.CompilerOptimizationSwitches |

| Debug                          | -gdwarf2                            |

| Size                           | -opt space                          |

| Speed                          | -opt speed                          |

| CompilerPath                   | d:\applications\CodeWarrior         |

For both toolchains these settings configure optimizations for speed, size, and debug. The settings are compiler specific. These properties can be edited from the **Target Support Package FM5 Target Preferences** dialog box or from the **Configuration Parameters** dialog box, described below. The defaults should be adequate for most rapid prototyping purposes.

If you want to alter these settings, consult your compiler documentation for specific optimizations. To edit the settings,

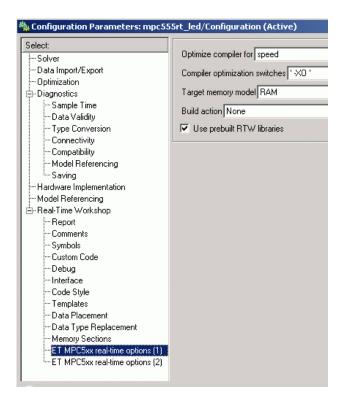

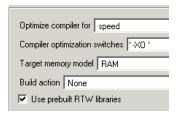

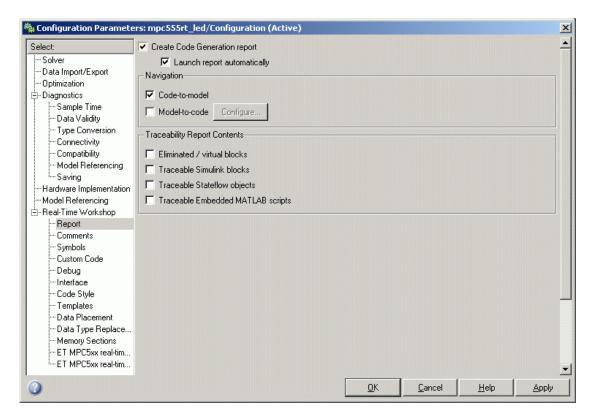

• If you want your changes to apply to many models, edit them within the Target Support Package FM5 Target Preferences dialog box. Your settings will appear within the Configuration Parameters dialog box in the Compiler optimization switches field when you select speed, size or debug from the Optimize compiler for options in the drop-down menu. You must choose ET MPC5xx real-time options (1) from the Real-Time Workshop tree to reach these settings, as shown in the following example.

• If you want to customize these settings for a single model, edit them from the **Configuration Parameters** dialog box. **Optimize compiler for** will change to custom and the defaults for these settings will remain unchanged in the **Target Support Package FM5 Target Preferences** dialog box. When you edit these settings, you must place single quotation marks at either end of the string. These settings are then applied to model code.

**Use Prebuilt RTW Libraries.** This check box option (selected by default) determines whether prebuilt RTW libraries, compiled with default compiler switches, are linked against during compilation of the generated code. When this option is not selected, the source modules that comprise these libraries will be compiled individually in the model build directory, using the currently selected compiler switches. Using prebuilt RTW libraries saves a considerable amount of time during the build process

## **Debugger Switches**

This setting is specific to Wind River Systems SingleStep. See "Setting Target Preferences for Wind River Compiler and Wind River Systems SingleStep<sup>TM</sup>" on page A-5.

# **Run Test Program**

To verify your setup, you can download and run a simple test program on the phyCORE-MPC555 board:

- 1 Select Start > Links and Targets > Target Support Package FM5 > Run Simple MPC555 Test Application.

- **2** To answer the question Do you want to run the application? Type y at the command line.

If you have not set up your target preferences properly the process will stop and ask you to do this now.

Watch as your toolchain downloads and runs the application on your phyCORE board. Successful execution results in a blinking LED.

You have now verified your installation and are ready to begin working with the Target Support Package FM5 product.

# **Download Boot Code to Flash Memory**

The next step is to download the boot code to flash memory, if you have not already done so. Normally, you will only need to program the boot code into flash memory once. After this is done, new application code can be downloaded as often as required without any changes to the boot code.

The first time you program the boot code into the target hardware, you must download it via the BDM port. However, if existing boot code is already programmed into flash memory and must be replaced (for example, with a newer or modified version) it is also possible to download entirely over CAN or serial. If you are upgrading from a previous release of the Target Support Package FM5 product you must download the new boot code.

If your target does not have bootcode already you can only install new bootcode with a BDM. See the next section "Installing Bootcode via BDM and Serial or CAN" on page 1-26. For existing bootcode, you can use a BDM or CAN; with bootcode from version 1.2 or later you can also download over Serial. See "Installing Bootcode Without a BDM" on page 1-27.

The first time you use the Target Support Package FM5 product you must use a toolchain to download boot code to the MPC555 flash memory. Once the boot code is loaded into flash memory, you can download code to the processor entirely over serial or the CAN network as described in the tutorials. See "Overview of Memory Organization and the Boot Process" on page 2-20 for more information.

## Installing Bootcode via BDM and Serial or CAN

To install bootcode, follow these steps:

- 1 Connect the BDM cable to the target, and a serial or CAN cable. If you do not have a BDM available, see "Installing Bootcode Without a BDM" on page 1-27.

- 2 Select Start > Links and Targets > Target Support Package FM5 > Install MPC5xx Bootcode.

A dialog appears asking if you are connected to the target via BDM. Read the information on the dialog.

3 Click Yes.

Your toolchain is launched and prepares to download.

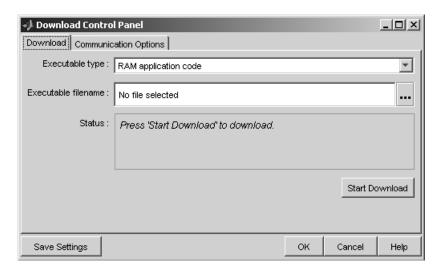

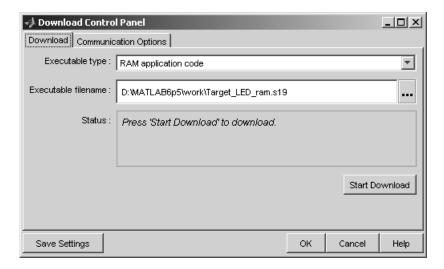

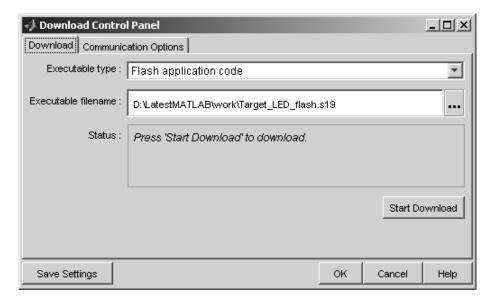

The **Download Control Panel** appears.

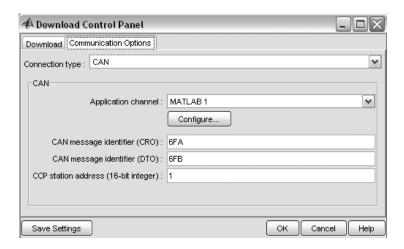

- 4 If you are using CAN (the default) you can proceed to step 5. If you are using serial to connect to the target, click the **Communications**Options tab in the **Download Control Panel** and select Serial from the Connection type drop-down menu.

- 5 On the Download tab, click Start Download.

Your development tools execute a command to install the boot code. When the process stops, the messages in the **Download Control Panel** complete, and the **Stop Download** button reverts to **Start Download**. The boot code should now be installed.

### **Installing Bootcode Without a BDM**

If your target does not have bootcode already you can only install new bootcode with a BDM. For targets with existing bootcode, if you do not have a BDM available you can install bootcode as follows:

- For a target with R14 bootcode, you can install new bootcode using the

Start menu exactly as described above except step 4 click No when asked

if you are connected via BDM. The download should complete successfully

over serial or CAN.

- If existing bootcode on the target is version 1.1 (R13+SP1), you can install

bootcode without a BDM if you have CAN. Use the **Start** menu bootcode

installer as described above and click **No** when asked if connected by BDM.

The download should complete successfully over CAN.

**Note** If the existing bootcode is earlier than version 1.1 (if it is R12.1 or R13), you need to upgrade bootcode with a BDM. If no BDM is available, please contact The MathWorks<sup>TM</sup> for a solution.

Once you have successfully downloaded boot code to your target, you have completed your installation and are ready to use all the features of the target support package. If necessary, please consult your toolchain documentation.

We suggest you now turn to Chapter 2, "Generating Stand-Alone Real-Time Applications" to get hands-on experience with using the Target Support Package FM5 product and your toolchain to generate, download, and execute application code on your phyCORE-MPC555 board. You can then also work through the tutorials in Chapter 3, "PIL Cosimulation" to start using processor-in-the-loop simulation for development via the Target Support Package FM5 product.

## **Start Menu Options**

You can use the **Start** menu for the following options:

- **MPC5xx Driver Library** Opens the MPC5xx Drivers block library. See "MPC555 Drivers" on page 4-2.

- CAN Message Blocks Opens the CAN Message Blocks library. See "CAN Message Blocks and CAN Drivers" on page 4-7.

- **CAN Drivers (Vector) Library** Opens the CAN Drivers (Vector) block library. See "CAN Message Blocks and CAN Drivers" on page 4-7.

- Target Preferences Opens the Target Preferences dialog. See "Setting Target Preferences" on page 1-18.

- Run Simple MPC5xx Test Application (via BDM) Downloads and runs a simple test application to blink an LED with your hardware. See "Run Test Program" on page 1-25.

- **Install MPC5xx Bootcode** Installs the appropriate boot code on your target processor. See "Download Boot Code to Flash Memory" on page 1-25.

- **Inspect the MPC5xx Hardware (via BDM)** Opens your debugger so you can inspect the hardware.

- **Debug RAM Based Application (via BDM)** Downloads and then allows you to debug a RAM application in .elf format.

- Debug FLASH Based Application Already in FLASH (via BDM) Allows you to debug an application (in .elf format) already in FLASH.

- Download RAM / FLASH Based Application (via CAN / Serial) Launches the Download Control Panel, for downloading applications in . s19 format to your hardware. See "Tutorial: Creating a New Application" on page 2-5, and "Downloading Application Code" on page 2-22.

- Download FLASH Based Application (via BDM and CAN / Serial)

— Allows you to use a BDM and the Download Control Panel to download an application in .s19 format to FLASH memory. See "Downloading Application Code" on page 2-22.

- Initialize visionPROBE for Selected Target Board (WindRiver Only) If you are using a visionPROBE, you must run this option to initialize the device, after setting target preferences (and again if you change target processor). See "Initialize visionPROBE" on page A-7.

- **Rebuild the MPC5xx Driver Library** Recompiles the MPC5xx Driver libraries. See "Boot Code Parameters for CAN Download" on page 2-29.

- **Environment Setup Help** Opens the Help Browser displaying the documentation for setting up and verifying your installation.

- **Help** Opens the Help Browser and displays the product documentation.

- **Demos** Opens the product demos help with links to open the demos.

- **Product Page (Web)** Opens the product page on The MathWorks web site.

## **Data Type Support and Scaling for Device Driver Blocks**

The following table summarizes the input and output data types supported by the device driver blocks in the Target Support Package<sup>TM</sup> FM5 library and the scaling applied to block inputs and outputs.

### I/O Data Types and Scaling for MPC5xx Device Driver Blocks

| Block                                 | Input Data<br>Type                | Input<br>Scaling                                     | Output Data<br>Type                                           | Output<br>Scaling/<br>Units                 |

|---------------------------------------|-----------------------------------|------------------------------------------------------|---------------------------------------------------------------|---------------------------------------------|

| MIOS Digital In                       |                                   |                                                      | Boolean                                                       | 0 or 1 only                                 |

| MIOS Digital<br>Out                   | Any Simulink® supported data type | logic 1 if<br>input > 0,<br>logic 0 if<br>input <= 0 |                                                               |                                             |

| MIOS<br>Digital Out<br>(MPWMSM)       | Any Simulink supported data type  | logic 1 if<br>input > 0,<br>logic 0 if<br>input <= 0 |                                                               |                                             |

| MIOS Pulse<br>Width<br>Modulation Out | double or single                  | 0 to 1                                               |                                                               |                                             |

| MIOS<br>Waveform<br>Measurement       |                                   |                                                      | double or single                                              | Seconds                                     |

| QADC Analog<br>In                     |                                   |                                                      | uint16 or int16<br>(defined by<br>Justification<br>parameter) | (defined by <b>Justification</b> parameter) |

| QADC Digital<br>In                    |                                   |                                                      | Boolean                                                       | 0 or 1 only                                 |

| TouCAN<br>Receive                     |                                   |                                                      | CAN_MESSAGE_STANDARD<br>or<br>CAN_MESSAGE_EXTENDED            | N/A                                         |

### I/O Data Types and Scaling for MPC5xx Device Driver Blocks (Continued)

| Block                                           | Input Data<br>Type                                 | Input<br>Scaling                            | Output Data<br>Type | Output<br>Scaling/<br>Units |

|-------------------------------------------------|----------------------------------------------------|---------------------------------------------|---------------------|-----------------------------|

| TouCAN<br>Transmit                              | CAN_MESSAGE_STANDARD<br>or<br>CAN_MESSAGE_EXTENDED | N/A                                         |                     |                             |

| TouCAN<br>Warnings                              |                                                    |                                             | Boolean             | N/A                         |

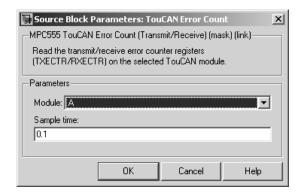

| TouCAN Error<br>Count                           |                                                    |                                             | uint8               | N/A                         |

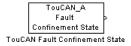

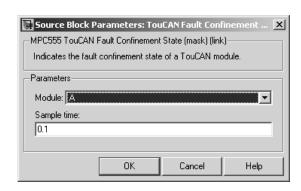

| TouCAN Fault<br>Confinement<br>State            |                                                    |                                             | uint16              | N/A                         |

| TPU3 Digital In                                 |                                                    |                                             | Boolean             | 0 or 1 only                 |

| TPU3 Digital<br>Out                             | Any Simulink<br>supported data type                | Logic 1 if input > 0, logic 0 if input <= 0 |                     |                             |

| TPU3 Fast<br>Quadrature<br>Decode               | Fast Mode input<br>Boolean                         |                                             | uint16              | N/A                         |

| TPU3 New Input Capture/Input Transition Counter |                                                    |                                             | uint16              | N/A                         |

| TPU3                                            |                                                    |                                             | Time Accumulation   | N/A                         |

| Programmable<br>Time                            |                                                    |                                             | uint32              |                             |

| Accumulator                                     |                                                    |                                             | Period Count        |                             |

|                                                 |                                                    |                                             | uint8               |                             |

### I/O Data Types and Scaling for MPC5xx Device Driver Blocks (Continued)

| Block                                 | Input Data<br>Type                                               | Input<br>Scaling                                 | Output Data<br>Type                                                                                   | Output<br>Scaling/<br>Units              |

|---------------------------------------|------------------------------------------------------------------|--------------------------------------------------|-------------------------------------------------------------------------------------------------------|------------------------------------------|

| TPU3 Pulse<br>Width<br>Modulation Out | Duty cycle input (top if 2 inputs): double or single             | 0 to 1                                           |                                                                                                       |                                          |

|                                       | Pulse period register input — uint16                             | Saturated<br>to be in the<br>range 0 to<br>32768 |                                                                                                       |                                          |

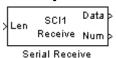

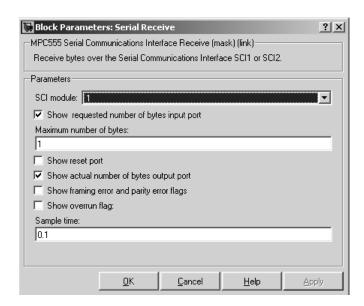

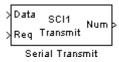

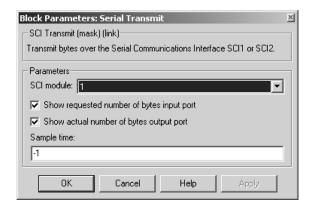

| Serial Transmit                       | Data: uint8 (vector or scalar)  Number of bytes: uint32 (scalar) | N/A                                              | Number of bytes: uint32                                                                               | 0-16 (for<br>SCI1); 0 or<br>1 (for SCI2) |

| Serial Receive                        | Number of bytes:<br>uint32<br>Reset: Boolean                     | N/A<br>0 or 1                                    | Data: uint8  Actual number of bytes: uint32  Framing and parity error: Boolean  Overrun flag: Boolean | N/A<br>N/A<br>0 or 1<br>0 or 1           |

### **Configuration Class Blocks**

Each sublibrary of the Target Support Package FM5 library contains a  $configuration\ class\ block$  that has an icon similar to the one shown in this figure.

Configuration class blocks exist only to provide information to other blocks. *Do not copy these objects into a model.*. If you do you see an error dialog box to warn you. This causes build failures.

# Generating Stand-Alone Real-Time Applications

This section includes the following topics:

Overview (p. 2-3) An overview of the Target Support

Package™ FM5 real-time target, other components required to generate stand-alone real-time applications, and the process of deploying generated code on target

hardware.

Tutorial: Creating a New Application

(p. 2-5)

A hands-on exercise in building an application from a demo model, including downloading and executing generated code on a target board.

Downloading Boot and Application

Code (p. 2-18)

A detailed discussion of the process of downloading code to the MPC555

RAM and flash memory.

Parameter Tuning and Signal

Logging (p. 2-32)

How use Simulink® external mode or a third party calibration tool for signal logging and parameter tuning.

HTML Code Profile (RAM/ROM)

Report (p. 2-46)

This section introduces the extended HTML code generation report.

Execution Profiling (p. 2-47) How to use the execution profiling

utilities to generate reports and graphical displays for analyzing timer-based tasks and asynchronous Interrupt Service Routines (ISRs).

Summary of the Real-Time Target

(p. 2-57)

Summary of the code generation options specific to the real-time target, and requirements and restrictions that apply to the current

release.

Suggestions for achieving higher Performance Tips (p. 2-61)

performance, for instance by using the Model Advisor, and increasing

System Clock speed.

### **Overview**

#### In this section...

"Generating Real-Time Applications" on page 2-3

"Deploying Generated Code" on page 2-4

## **Generating Real-Time Applications**

This section describes how to generate a stand-alone real-time application for the MPC555. The components required to generate stand-alone code are

- The Target Support Package<sup>TM</sup> FM5 real-time target features

- The MPC555 Resource Configuration object provided in the Target Support Package FM5 library

- I/O driver blocks provided in the Target Support Package FM5 library

- Utilities for downloading generated code to the target hardware

Using these together with your toolchain, you can build a complete application. You do not need to hand-write any C code to integrate the generated code into a final application.

See "Before You Begin" on page 2-6 for information on supported hardware and toolchains.

The tutorial "Tutorial: Creating a New Application" on page 2-5 uses two blocks from the Target Support Package FM5 library. For complete information on the Target Support Package FM5 library blocks, see Chapter 4, "Block Reference".

Before reading this section and using the Target Support Package FM5 library, you should have at least a basic understanding of the architecture of the MPC555. To learn about the MPC555, we suggest that you study the MPC555 Users Manual. We recommend that you read the introduction to the processor and familiarize yourself with all the major subsystems of the MPC555. You can find this document at the following URL:

http://www.freescale.com/files/microcontrollers/doc/user\_guide/MPC555UM.pdf

## **Deploying Generated Code**

You can load a generated program into the MPC555 flash memory for permanent deployment. You can also load your code into external RAM (if available on your development hardware).

Alternatively, you can use the automatic code generation process for rapid prototyping and investigate a range of different design alternatives before making a deployment decision.

Your generated program can run on any Electronic Control Unit (ECU) that is based on the MPC5xx processor. Your application can use any of the supported MPC5xx on-chip I/O devices. We provide driver blocks for the MPC5xx's MIOS, TPU, QADC and TouCAN modules, providing you with drivers for the on-chip analog input, digital I/O, PWM, serial and CAN devices.

See Chapter 4, "Block Reference" for further information on the device driver blocks in the Target Support Package FM5 library.

In addition to on-chip I/O resources, an ECU typically provides additional I/O devices. If you want to access such custom I/O devices, you must write device drivers and integrate them with the automatically generated code. See the following documentation for details:

- Real-Time Workshop® User's Guide

- $\bullet \ \ Real\text{-}Time \ Workshop ^{\circledR} \ Embedded \ Coder ^{\tiny \mathsf{TM}} \ User's \ Guide$

- Writing S-Functions

Once the application has been programmed into memory on the target system, you may need to monitor signals or tune parameters. The Target Support Package FM5 product supports signal monitoring and parameter tuning via Simulink® external mode or a third party calibration tool. In both cases you must include a CAN Calibration Protocol (CCP) block in your model. The CAN Calibration Protocol block implementation of CCP has been tested against CANape from Vector-Informatik and ATI Vision. See "Parameter Tuning and Signal Logging" on page 2-32 and CAN Calibration Protocol (MPC555) for further information.

## **Tutorial: Creating a New Application**

#### In this section...

"Tutorial Overview" on page 2-5

"Before You Begin" on page 2-6

"The Example Model" on page 2-7

"Generating Code" on page 2-10

"Downloading the Application to RAM via Serial or CAN" on page 2-12

"Downloading the Application to RAM via BDM" on page 2-16

### **Tutorial Overview**

In this tutorial, you build a stand-alone real-time application from a model incorporating blocks from the Target Support Package™ FM5 library. We assume that you are already familiar with the Simulink® product and with the Real-Time Workshop® code generation and build process.

In the following sections, you will

- Configure the model

- Generate code from a subsystem

- Download code by one of the following methods:

- Download to target RAM via a serial connection, using the **Download** Control Panel utility (provided with the Target Support Package FM5 product)

- Download to target RAM via a CAN connection, using the **Download** Control Panel utility

- Download to target RAM via a BDM connection

- Execute the code on the target

After you complete this tutorial, you may want to learn how to deploy generated code into the MPC555 flash memory. See "Downloading Boot and Application Code" on page 2-18 for that information.

## **Before You Begin**

This tutorial requires the following specific hardware and software in addition to the Target Support Package FM5 product:

Phytec phyCORE-MPC555 development board

The tutorial model utilizes two LEDs on the phyCORE-MPC555 board. These LEDs are connected to pins MPI032B0 and MPI032B1 on the MPC555 MIOS digital output pins. If you are using a different development board, you may be able to obtain the same functionality by making similar connections.

- A supported toolchain for compiling and debugging. Currently supported toolchains are

- Wind River Compiler and Wind River Systems SingleStep<sup>TM</sup> from Wind River Systems

- CodeWarrior® from Freescale™

See "Setting Up Your Toolchain" on page A-3 for details.

- Hardware to enable downloading:

- If you want to download generated code to the target board over serial you will need a serial cable to connect your host PC to the target board.

- If you want to download over BDM you will need a BDM device.

- If you want to download via CAN, you will need a supported CAN card and drivers from Vector-Informatik. See "CAN Hardware and Drivers" on page A-20.

### **Configuring Target Preferences and Boot Code**

- Make sure that your target preferences are set correctly for your development tools. See "Setting Target Preferences" on page 1-18.

- Once your target preferences are set for your toolchain you must download bootcode to the target before you can work through this tutorial. See "Download Boot Code to Flash Memory" on page 1-25.

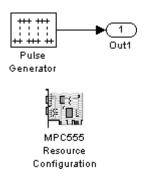

## The Example Model

In this tutorial we will use a simple example model, mpc555rt\_led, from the directory matlabroot/toolbox/rtw/targets/mpc555dk/mpc555demos.

This directory is on the default MATLAB® path. The path <code>matlabroot</code> is the location where MATLAB is installed.

1 Open the model.

mpc555rt led

**2** Save a local copy to your working directory. We will work with this copy throughout this exercise.

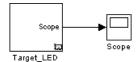

mpc555rt\_led\_demo Model, Root Level on page 2-7 shows the example model at the root level. We will only use this level in simulation.

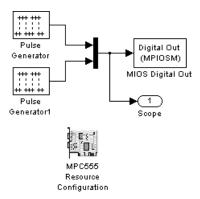

mpc555rt\_led\_demo Model, Root Level

3 Double-click on the Target LED subsystem block.

Target\_LED Subsystem on page 2-7 shows the Target\_LED subsystem, from which we will generate code.

Target\_LED Subsystem

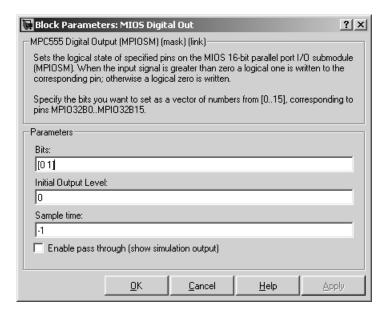

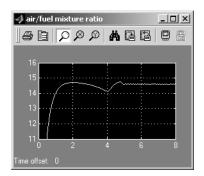

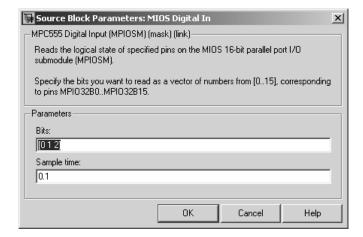

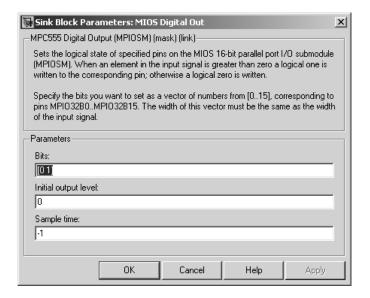

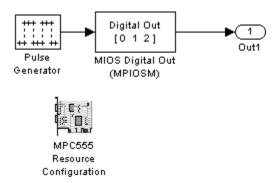

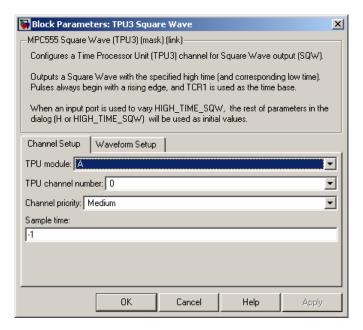

In the Target\_LED subsystem, two square wave signals are multiplexed and routed to the MIOS Digital Out block. The MIOS Digital Out block accepts a vector of numbers representing pins 0-15 on the MIOS 16-bit Parallel Port I/O Submodule (MPIOSM) on the MPC555. As the square wave signals oscillate between 0 and 1, the MIOS Digital Out block writes corresponding logic values to the appropriate pin on the port.

This figure shows the parameters of the MIOS Digital Out block.

The **Bits** field is set to the vector [0 1]. The block maps this vector to the MPC555 MIOS digital output pins MPI032B0 and MPI032B1. When the application runs, it will send a pulse signal to these output pins. On the phyCORE-MPC555 board, these signals are connected to two of the LEDs, which will switch on and off at the frequency set in the respective pulse generator blocks.

In addition to the Pulse Generator, Mux, MIOS Digital Out, and Output blocks, the Target\_LED subsystem contains a MPC555 Resource Configuration object. When building a model with driver blocks from the Target Support Package FM5 library, you must always place a MPC555 Resource Configuration object into the model (or the subsystem from which you want to generate code) first.

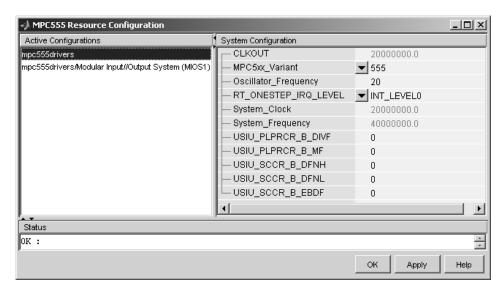

The purpose of the MPC555 Resource Configuration object is to provide information to other blocks in the model. Unlike conventional blocks, the MPC555 Resource Configuration object is not connected to other blocks via input or output ports. Instead, driver blocks (such as the MIOS Digital Out block in the example model) query the MPC555 Resource Configuration object for required information.

For example, a driver block may need to find the system clock speed that is configured in the MPC555 Resource Configuration object. The MPC555 has a number of clocked subsystems; to generate correct code, driver blocks need to know the speeds at which these clock busses will run.

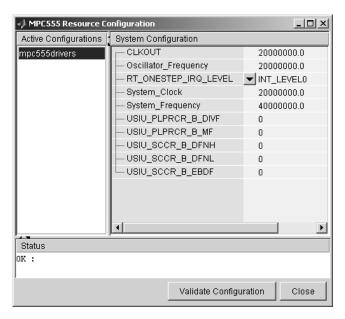

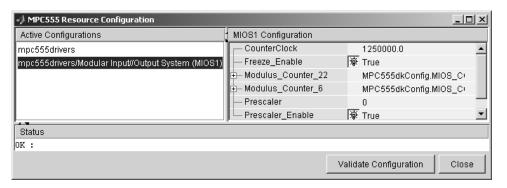

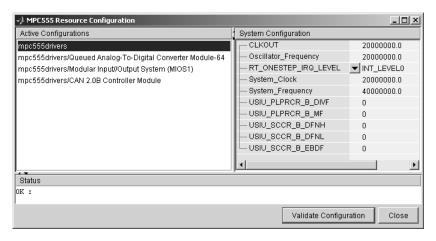

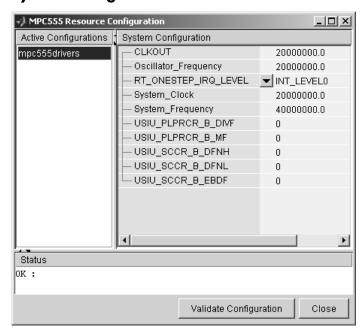

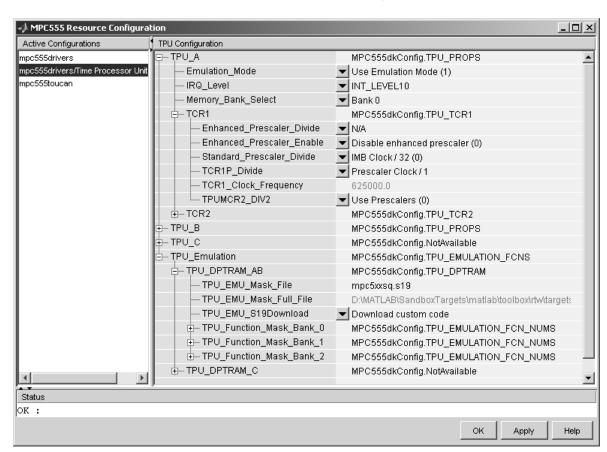

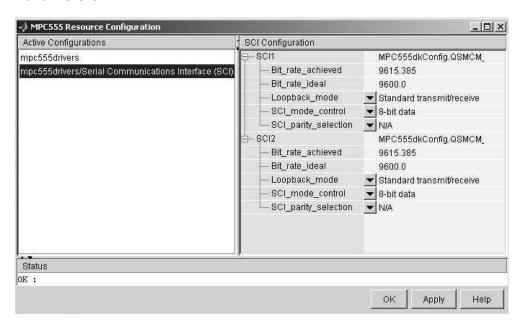

The MPC555 Resource Configuration window lets you examine and edit the MPC555 Resource Configuration settings. To open the MPC555 Resource Configuration window, double-click on the MPC555 Resource Configuration icon. This figure shows the **MPC555 Resource Configuration** window for the Target\_LED subsystem.

In this tutorial, we will use the default MPC555 Resource Configuration settings. Observe, but do not change, the parameters in the MPC555 Resource Configuration window. To learn more about the MPC555 Resource Configuration object, see MPC555 Resource Configuration.

Close the MPC555 Resource Configuration window before proceeding.

The next step in this tutorial is generating code.

### **Generating Code**

We will now look at settings and then generate application code:

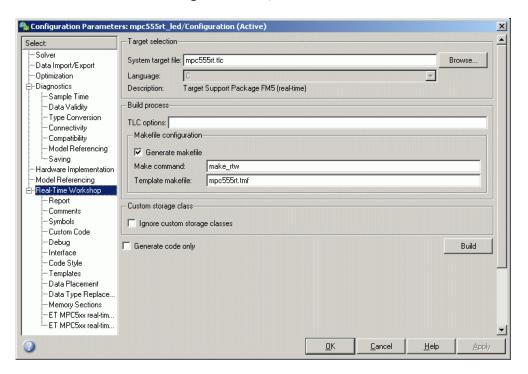

- 1 Select Simulation > Configuration Parameters. The Configuration Parameters dialog opens.

- **2** Select **Real-Time Workshop** in the tree, as shown below.

**3** Notice the **RTW** system target file for real-time deployment is mpc555rt.tlc.

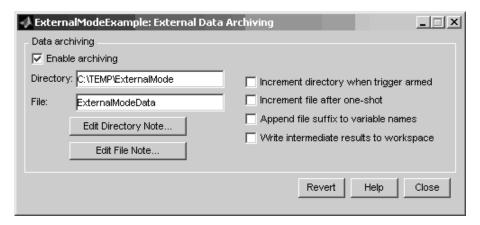

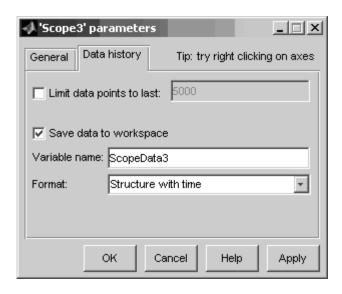

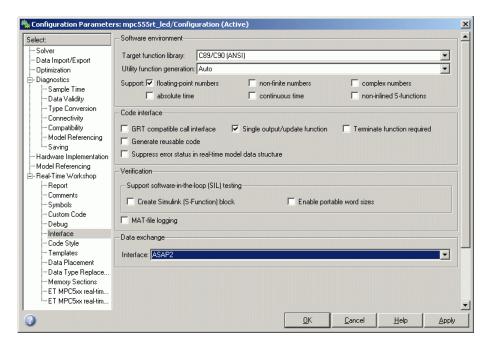

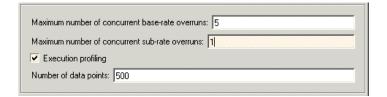

To see how to change from real-time deployment to processor-in-the-loop or algorithm export, click on the **Browse** button to open the **System Target**